## OKI semiconductor

## MSM51C262

High Performance Low Power 64K x 4 Multi-port Memory with Fast Page Mode

## **GENERAL DESCRIPTION**

The OKI MSM51C262 is a high speed 65,536 x 4-bit multiport CMOS dynamic memory. The two ports, random access and serial access, are configured to offer optimum flexibility in graphics and other systems that require an interface between a processor and a high speed serial data channel such as a CRT or graphics display device.

The organization of the random access port of the MSM51C262 is exactly like, a 64K x 4 CMOS DRAM. Additional functions such as transfer between RAM and SAM (serial access memory) use otherwise unused states of the CAS, DT/OE, WB/WE and SE signals sampled at the falling edge of RAS at the beginning of a cycle.

SAM is organized as  $256 \times 4$  bits that can be read or written at high speed. The contents of SAM can be loaded into RAM, and the contents of a selected RAM row ( $256 \times 4$ ) can be loaded into SAM. Except when transferring data between one another, SAM and RAM operate in an asynchronous manner. The transfer from RAM to SAM or SAM to RAM also refreshes the transferred row in the RAM.

In a RAM to SAM load cycle, 8 bits are needed to specify which of the 256 rows is to be transferred. The state of the address lines at the falling edge of CAS is used to specify the starting point in SAM where data is to be written or read. The static mechanization of the SAM (allowed by CMOS) does not require refreshing. The first access to SAM, either read or write, is to the location specified at CAS time in the previous cycle, and subsequent accesses continue in an increasing address direction, module 256.

The MSM51C262 is processed using OKI's CMOS silicon gate process technology. This advanced CMOS processing allows memory devices to be fabricated with lower operating current and higher performance than comparable NMOS designs. All I/O signals are TTL compatible. Input and I/O capacitances are significantly lowered to enhance system performance.

П

#### ■ MSM51C262 ■ -

## **FEATURES**

- Low power dissipation for MSM51C262-12

- RAM port operating alone 50 mA

- SAM port operating alone 35 mA

- RAM/SAM operating 5 together

85 mA

- Low CMOS standby current 6 mA

- Fast Page Mode access, RAS-Only Refresh, and CAS-before-RAS Refresh capability

- Bi-directional data transfer between RAM and SAM with real-time operation.

- Bit-masked Write function on RAM port for additional flexibility.

- 256 Refresh cycle/4 ms.

- Standard package is 24 pin 400 mil Plastic ZIP.

| High Performance MSM51C262                          | - 80   | - 10   | - 12   |

|-----------------------------------------------------|--------|--------|--------|

| Max. RAS Access Time (t <sub>RAC</sub> )            | 80 ns  | 100 ns | 120 ns |

| Max. Column Address Time (t <sub>CAA</sub> )        | 40 ns  | 45 ns  | 55 ns  |

| Min. Fast Column Mode Cycle Time (t <sub>PC</sub> ) | 55 ns  | 60 ns  | 70 ns  |

| Min. Read/Write Cycle Time (t <sub>RC</sub> )       | 145 ns | 175 ns | 205 ns |

| Min. Serial Port Cycle Time (t <sub>SCC</sub> )     | 30 ns  | 35 ns  | 40 ns  |

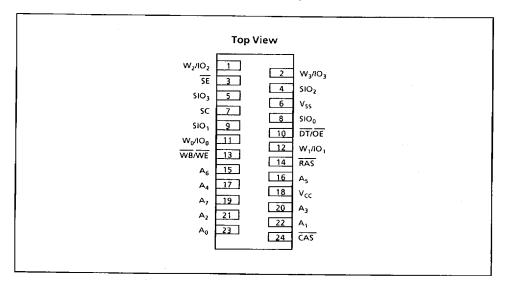

## 24 LEAD PLASTIC ZIP PIN CONFIGURATION

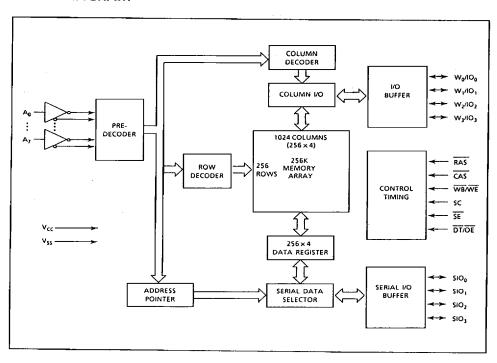

## **BLOCK DIAGRAM**

## **ELECTRICAL CHARACTERISTICS**

## **ABSOLUTE MAXIMUM RATINGS\***

| Rating                                                                | Value          | Unit |

|-----------------------------------------------------------------------|----------------|------|

| Ambient Temperature Under Bias                                        | 0 to 70        | °C   |

| Storage Temperature (Plastic)                                         | - 55 to + 125  | °C   |

| Voltage on any Pin Except V <sub>CC</sub> Relative to V <sub>SS</sub> | - 1.0 to + 7.0 | V    |

| Voltage on V <sub>CC</sub> Relative to V <sub>SS</sub>                | - 1.0 to + 7.0 | V    |

| Data Output Current                                                   | 50             | mA   |

| Power Dissipation                                                     | 1.0            | w    |

<sup>\*</sup> Operation at or above ABSOLUTE MAXIMUM RATINGS can adversely affect device reliability.

## **AC TEST CONDITIONS**

| Conditions                     | Value                     | Unit |

|--------------------------------|---------------------------|------|

| Input Rise Levels              | 0 to 3.0                  | ٧    |

| Input Rise and Fall Times      | 5 between 0.8 V and 2.4 V | ns   |

| Input Timing Reference Levels  | 0.8 and 2.4               | ٧    |

| Output Timing Reference Levels | 0.8 and 2.4               | ٧    |

| Output Load (RAM Port)         | 2 TTL (and 100)           | pF   |

| Output Load (SAM Port)         | 2 TTL (and 50)            | pF   |

## **CAPACITANCE\***

$T_A = 25$ °C,  $V_{CC} = 5 \text{ V} \pm 10\%$ ,  $V_{SS} = 0 \text{ V}$

| Symbol           | Parameter                                  | Тур. | Max. | Unit |

|------------------|--------------------------------------------|------|------|------|

| C <sub>IN1</sub> | Address Input Capacitance                  |      | 5    | pF   |

| C <sub>IN2</sub> | RAS, CAS, WB/WE, SE, SC, DT/OE Capacitance |      | 8    | pF   |

| C <sub>OUT</sub> | I/O Capacitance                            |      | 7    | pf   |

<sup>\*</sup> Capacitance is sampled and not 100% tested.

## DC CHARACTERISTICS (1)

( $T_A = 0$ °C to 70°C,  $V_{CC} = 5$  V  $\pm$  10%,  $V_{SS} = 0$  V, unless otherwise specified.)

|                                                        | Sym-                                             |                                                                                                           | Access | мѕмѕ     | 1C262 |      |       |

|--------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------|----------|-------|------|-------|

| Parameter                                              | bol                                              | Conditions                                                                                                | Time   | Min.     | Max.  | Unit | Notes |

| Input Leakage Current<br>(Any Input Pin)               | ارز                                              | V <sub>SS</sub> < V <sub>IN</sub> < V <sub>CC</sub>                                                       |        | - 10     | 10    | μΑ   |       |

| Output Leakage Current<br>(For High-Z State)           | lro                                              | $V_{SS} < V_{OUT} < V_{CC}$<br>RAS, CAS and SE at $V_{IH}$                                                |        | - 10     | 10    | μΑ   |       |

|                                                        |                                                  | RAS/CAS Cycling, SAM Port                                                                                 | 80     |          | 70    |      |       |

| V <sub>CC</sub> Supply Current                         | I <sub>CC1</sub>                                 | TTL Standby                                                                                               | 100    |          | 60    | mA   | 2,3   |

|                                                        |                                                  | t <sub>RC</sub> (min.), SC = V <sub>IL</sub>                                                              | 120    | <u> </u> | 50    | L    |       |

| V <sub>CC</sub> Supply Current,<br>TTL Stanbdy         | I <sub>CC2</sub>                                 | RAM/SAM Ports TTL <u>Standby</u> RAS, CAS at V <sub>IH</sub> , I/O > V <sub>SS</sub> SC = V <sub>IL</sub> |        |          | 8     | mA   |       |

| V <sub>CC</sub> Supply Current,                        |                                                  | RAS Cycling, CAS at V <sub>IH</sub>                                                                       | 80     |          | 70_   |      |       |

| RAS-Only Refresh                                       | l <sub>CC3</sub>                                 | SAM Port TTL Standby                                                                                      | 100    |          | 60    | mA   | 2, 3  |

|                                                        |                                                  | $t_{RC}$ (min.), $SC = V_{IL}$                                                                            | 120    |          | 50    |      |       |

| V Supply Current                                       |                                                  | RAS = V <sub>IL</sub> , CAS Cycling                                                                       | 80     |          | 60    |      |       |

| V <sub>CC</sub> Supply Current,<br>Page Mode Operation | I <sub>CC4</sub>                                 | SAM Port TTL Standby                                                                                      | 100    | 1        | 50    | mA   | 2, 3  |

|                                                        |                                                  | $t_{PC}$ (min.), $SC = V_{IL}$                                                                            | 120    |          | 40    | 1    |       |

| V. Supply Cyrrent                                      | <b>—</b>                                         | RAS/CAS Cycling,                                                                                          | 80     |          | 70    | -    |       |

| V <sub>CC</sub> Supply Current,<br>CAS-before-RAS      | I <sub>CC5</sub>                                 | SAM Port TTL Standby                                                                                      | 100    | 1        | 60    | mA   | 2, 3  |

| Refresh                                                |                                                  | $t_{RC}$ (min.), $SC = V_{IL}$                                                                            | 120    |          | 50    | 1    |       |

| V <sub>CC</sub> Supply Current,                        |                                                  | RAS/CAS Cycling, SAM Port                                                                                 | 80     |          | 75    |      |       |

| RAM/SAM                                                | I <sub>CC6</sub>                                 | TTL Standby                                                                                               | 100    |          | 65    | mA   | 2, 3  |

| Transfer Mode                                          |                                                  | $t_{RC}$ (min.), $SC = V_{IL}$                                                                            | 120    |          | 55    |      |       |

| V <sub>CC</sub> Supply Current,                        | <b></b>                                          | RAS/CAS Cycling, SAM Port                                                                                 | 80     |          | 120   |      |       |

| Both Ports Active                                      | lccz                                             | Active                                                                                                    | 100    |          | 100   | ] mA | 2, 3  |

|                                                        | "()                                              | t <sub>RC</sub> (min.), t <sub>SCC</sub> (min.)                                                           | 120    |          | 85    |      |       |

| V Supply Cyrrent                                       | 1 -                                              | RAS/CAS at V <sub>IH</sub> , I/O > V <sub>SS</sub>                                                        | 80     |          | 50    |      |       |

| V <sub>CC</sub> Supply Current,<br>SAM-Only Operation  | I <sub>CC8</sub>                                 | SAM Port Active                                                                                           | 100    | 1        | 40    | mA   | 2     |

| or mir only operation                                  | 1.00                                             | t <sub>SCC</sub> (min.)                                                                                   | 120    |          | 35    | 1    | -     |

| M. Summly Compact                                      | †                                                | RAS Cycling, CAS at V <sub>IH</sub> ,                                                                     | 80     | 1        | 120   |      | T     |

| RAS-Only Refresh and ICC9 SAM Port Act                 | SAM Port Active                                  | 100                                                                                                       | +-     | 100      | mA    | 2, 3 |       |

|                                                        | t <sub>RC</sub> (min.), t <sub>SCC</sub> (min.)  | 120                                                                                                       |        | 85       | 1     |      |       |

| V. Sunday Courses                                      | <del>                                     </del> | $\overline{RAS} = V_{IL}, \overline{CAS}$ Cycling                                                         | 80     | $\top$   | 100   |      |       |

| 90                                                     | A . A A                                          | 100                                                                                                       |        | 90       | _     | 2,3  |       |

| and SAM Active                                         | , againtag aparaman   iccito                     |                                                                                                           | 120    |          | 75    |      |       |

## DC CHARACTERISTICS (CONT.)

|                                         | Sym-                                            |                                                 | Access | MSMS | 1C262      | Unit     | Notes |

|-----------------------------------------|-------------------------------------------------|-------------------------------------------------|--------|------|------------|----------|-------|

| Parameter                               | bol                                             | Conditions                                      | Time   | Min. | Max.       | Onic     | Mores |

| V <sub>CC</sub> Supply Current,         |                                                 | RAS/CAS Cycling,                                | 80     |      | 120        |          |       |

| CAS-before-RAS                          | I <sub>CC11</sub>                               | SAM Port Active                                 | 100    |      | 100        | mΑ       | 2, 3  |

| Refresh and SAM Active                  |                                                 | t <sub>RC</sub> (min.), t <sub>SCC</sub> (min.) | 120    |      | 85         |          |       |

| V <sub>CC</sub> Supply Current,         | RAS/CAS Cycling,                                |                                                 | 80     |      | 125        |          |       |

| RAM/SAM Transfer<br>Mode and SAM Active | I <sub>CC12</sub>                               | SAM Port Active                                 | 100    |      | 105        | mA       | 2, 3  |

|                                         | t <sub>RC</sub> (min.), t <sub>SCC</sub> (min.) | 120                                             |        | 90   |            |          |       |

| V <sub>CC</sub> Supply Current,         |                                                 | RAS, CAS, SE, WB/WE,                            | 80     |      | . 6        |          |       |

| Both Ports CMOS                         | I <sub>CC13</sub>                               | DT/OE > V <sub>CC</sub> - 0.5 V                 | 100    |      | 6          | mΑ       |       |

| Standby                                 |                                                 | SC<0.6 V                                        | 120    |      | 6          | 1        |       |

| Input Low Voltage                       | VIL                                             | 1                                               |        | - 1  | 0.8        | ٧        |       |

| Input High Voltage                      | V <sub>IH</sub> .                               |                                                 |        | 2.4  | VCC<br>+ 1 | >        |       |

| Output Low Voltage                      | VOL                                             | I <sub>OL</sub> = 4.2 mA                        |        | 1    | 0.4        | <b>V</b> |       |

| Output High Voltage                     | V <sub>ОН</sub>                                 | I <sub>OH</sub> = -2 mA                         |        | 2.4  |            | >        |       |

## AC CHARACTERISTICS (4, 5, 6) READ, WRITE, READ-MODIFY-WRITE AND REFRESH CYCLES

( $T_A = 0$ °C to 70°C,  $V_{CC} = 5$  V  $\pm$  10%,  $V_{SS} = 0$  V, unless otherwise specified.)

| Parameter.                        | Sym-             | -    | 80   | _    | 10   | - 12 |      | Unit | Notes |

|-----------------------------------|------------------|------|------|------|------|------|------|------|-------|

| Parameter                         | bol              | Min. | Мах. | Min. | Max. | Min. | Max. | Unit | Notes |

| Transition Time (Rise and Fall)   | t <sub>T</sub>   | 3    | 25   | 3    | 25   | 3    | 25   | ns   | ·     |

| Refresh Interval (256 Cycles)     | t <sub>Ri</sub>  |      | 4    |      | 4    |      | 4    | ms   |       |

| Read or Write Cycle Time          | t <sub>RC</sub>  | 145  |      | 175  |      | 205  |      | ns   |       |

| RAS Pulse Width                   | t <sub>RAS</sub> | 80   | 37K  | 100  | 37K  | 120  | 37K  | ns   |       |

| RAS Precharge Time                | t <sub>RP</sub>  | 55   |      | 65   |      | 75   |      | ns   |       |

| CAS Hold Time                     | t <sub>CSH</sub> | 80   |      | 100  |      | 120  |      | ns   |       |

| CAS Pulse Width                   | t <sub>CAS</sub> | 25   |      | 30   |      | 35   |      | ns   |       |

| Row Address Setup Time            | t <sub>ASR</sub> | 0    |      | 0    |      | 0    |      | ns   |       |

| Row Address Hold Time             | t <sub>RAH</sub> | 15   |      | 15   |      | 15   |      | ns   |       |

| CAS to RAS Precharge Time         | t <sub>CRP</sub> | 10   |      | 10   |      | 10   |      | ns   |       |

| RAS to CAS Delay                  | t <sub>RCD</sub> | 25   | 55   | 25   | 70   | 25   | 85   | ns   | 7     |

| Column Address Setup Time         | t <sub>ASC</sub> | 0    |      | 0    |      | 0    |      | ns   |       |

| Column Address Hold Time          | t <sub>CAH</sub> | 15   | i    | 20   |      | 20   |      | ns   |       |

| RAS Hold Time                     | t <sub>RSH</sub> | 25   |      | 30   | 1    | 35   |      | ns   |       |

| DT High Setup Time                | t <sub>DHS</sub> | 0    |      | 0    |      | 0    |      | ns   |       |

| DT High Hold Time                 | t <sub>DHH</sub> | 20   |      | 20   |      | 20   |      | ns   |       |

| Column Address Hold Time from RAS | t <sub>AR</sub>  | 60   |      | 70   |      | 80   |      | ns   |       |

## AC CHARACTERISTICS (CONT.)

## READ CYCLE

|                                          | Sym-             | _    | 80   | _    | 10   | _    | 12   |    | Notes       |

|------------------------------------------|------------------|------|------|------|------|------|------|----|-------------|

| Parameter                                | bol              | Min. | Max. | Min. | Мах. | Min. | Max. |    | Mores       |

| RAS Access Time                          | t <sub>RAC</sub> |      | 80   |      | 100  |      | 120  | ns | 8, 9        |

| CAS Access Time                          | t <sub>CAC</sub> |      | 25   |      | 30   |      | 35   | ns | 9,10,<br>11 |

| Column Address Access Time               | t <sub>CAA</sub> |      | 40   |      | 45   |      | 55   | ns | 9           |

| Read Command Setup Time                  | t <sub>RCS</sub> | 0    |      | 0    |      | 0    |      | ns |             |

| Read Command Hold Time RAS-Referenced    | t <sub>RRH</sub> | 5    |      | 5    |      | 10   |      | ns | 12          |

| Read Command Hold Time<br>CAS-Referenced | t <sub>RCH</sub> | 0    |      | 0    |      | 0    |      | ns | 12          |

| OE Access Time                           | toac             |      | 20   |      | 25   |      | 30   | ns | 9           |

| OE or CAS to Output High-Z               | t <sub>HZ</sub>  |      | 20   |      | 25   |      | 30   | ns | 13          |

| OE or CAS to Output Low-Z                | t <sub>LZ</sub>  | 0    |      | 0    |      | 0    |      | ns |             |

| Output Hold Time from OE or CAS          | toH              | 0    |      | 0    |      | 0    |      | ns |             |

|                                | Sym-             | _    | 80   | _    | 10   |      | 12   | Unit | Notes |

|--------------------------------|------------------|------|------|------|------|------|------|------|-------|

| Parameter                      | bol              | Min. | Max. | Min. | Max. | Min. | Max. |      | Notes |

| Write Command to RAS Lead Time | t <sub>RWL</sub> | 25   |      | 30   |      | 35   |      | ns   |       |

| Write Command to CAS Lead Time | t <sub>CWL</sub> | 25   |      | 30   |      | 35   |      | ns   |       |

| Write Command Pulse Width      | t <sub>WP</sub>  | 15   |      | 20   |      | 25   |      | ns   |       |

| Write Command Setup Time       | t <sub>WCs</sub> | 0    |      | 0    |      | 0    |      | ns   | 14    |

| Write Command Hold Time        | t <sub>WCH</sub> | 15   |      | 20   |      | 25   |      | กร   |       |

| Data In Setup Time             | tos              | 0    |      | 0    |      | 0    |      | ns   |       |

| Data In Hold Time              | t <sub>DH</sub>  | 15   |      | 20   |      | 25   |      | ns   |       |

| Write Mask Setup Time          | t <sub>WBS</sub> | 0    |      | 0    |      | 0    |      | ns   |       |

| Write Mask Hold Time           | t <sub>WBH</sub> | 20   |      | 20   |      | 20   |      | ns   |       |

| Write Mask Select Setup Time   | tws              | 0    |      | 0    |      | 0    |      | ns   |       |

| Write Mask Select Hold Time    | t <sub>WH</sub>  | 20   |      | 20   |      | 20   |      | ns   |       |

| OE Hold Time Referenced to WE  | toeh             | 10   |      | 10   |      | 15   |      | ns   |       |

| Write Hold Time from RAS       | t <sub>WCR</sub> | 65   |      | 80   |      | 95   |      | ns   |       |

| Data Hold Time from RAS        | t <sub>DHR</sub> | 65   |      | 80   |      | 95   |      |      |       |

## **READ-MODIFY-WRITE CYCLE**

| _                            | Sym-             | -    | 80   | - 10 |      | - 12 |      | ttnit | Notes |

|------------------------------|------------------|------|------|------|------|------|------|-------|-------|

| Parameter                    | bol              | Min. | Max. | Min. | Мах. | Min. | Max. |       | Notes |

| Read-Modify-Write Cycle Time | t <sub>RWC</sub> | 205  |      | 245  |      | 285  |      | ns    |       |

| RMW Cycle RAS Pulse Width    | t <sub>RRW</sub> | 140  | 37K  | 170  | 37K  | 200  | 37K  | ns    |       |

| RMW Cycle CAS Pulse Width    | t <sub>CRW</sub> | 85   |      | 100  |      | 115  |      | ns    |       |

| RAS to WE Delay              | t <sub>RWD</sub> | 110  |      | 135  |      | 160  |      | ns    | 14    |

| CAS to WE Delay              | t <sub>CWD</sub> | 55   |      | 65   |      | 75   |      | ns    | 14    |

| Column Address to WE Delay   | t <sub>AWD</sub> | 70   |      | 80   |      | 95   |      | ns    |       |

| OE to Data In Delay Time     | toED             | 20   |      | 25   |      | 30   |      | ns    |       |

# AC CHARACTERISTICS (CONT.) FAST PAGE MODE OPERATION

| Parameter                         | Sym-<br>bol      | - 80 |      | - 10 |      | - 12 |      |    | Notes |

|-----------------------------------|------------------|------|------|------|------|------|------|----|-------|

|                                   |                  | Min. | Max. | Min. | Max. | Min. | Мах. |    | Notes |

| Page Mode Cycle Time              | tpC              | 55   |      | 60   |      | 70   |      | ns |       |

| CAS Precharge Time                | t <sub>CP</sub>  | 15   |      | 20   |      | 25   |      | ns |       |

| Access Time from Column Precharge | t <sub>CAP</sub> |      | 50   |      | 55   |      | 65   | ns | 15    |

## CAS-BEFORE-RAS REFRESH CYCLE

| Parameter                         | Sym-<br>bol      | - 80 |      | - 10 |      | - 12 |      | Unit | Notes |

|-----------------------------------|------------------|------|------|------|------|------|------|------|-------|

|                                   |                  | Min. | Мах. | Min. | Мах. | Min. | Мах. |      | Notes |

| CAS-before-RAS Refresh Setup Time | t <sub>CSR</sub> | 10   |      | 10   |      | 10   |      | ns   |       |

| CAS-before-RAS Refresh Hold Time  | t <sub>CHR</sub> | 25   |      | 25   |      | 25   |      | ns   |       |

| RAS Precharge to CAS Active Time  | t <sub>RPC</sub> | 0    |      | 0    |      | 0    |      | ns   |       |

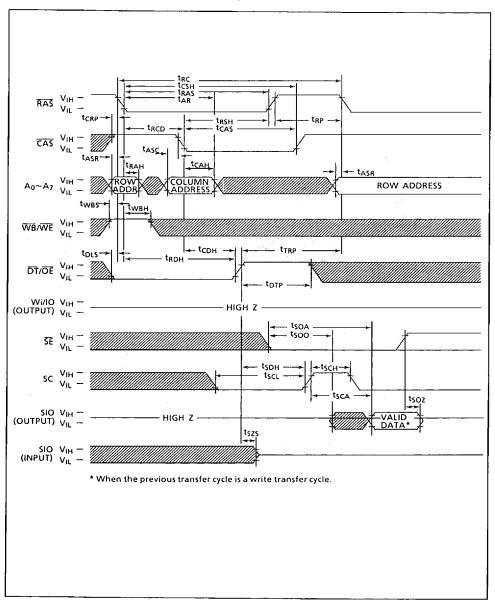

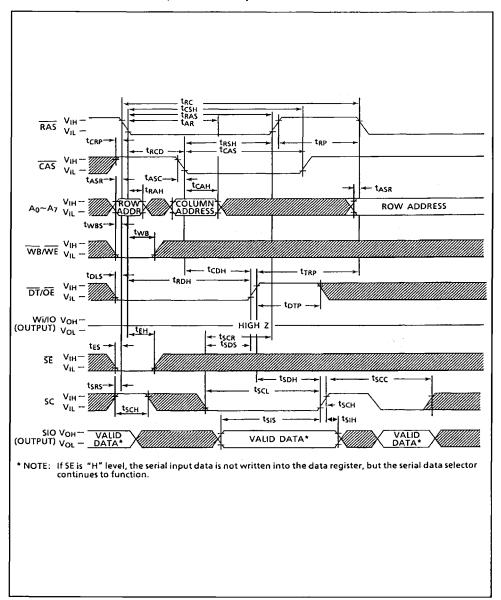

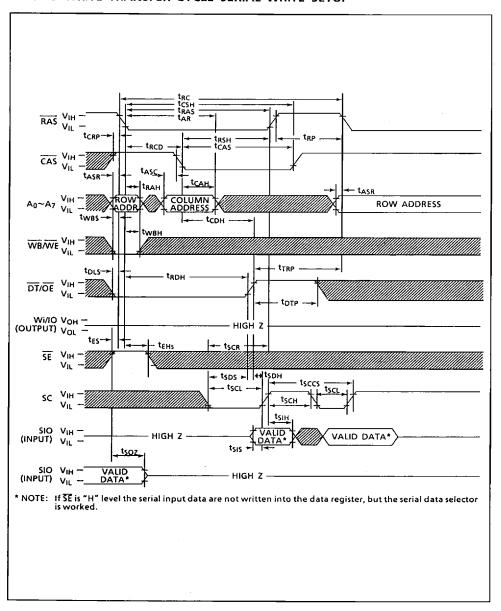

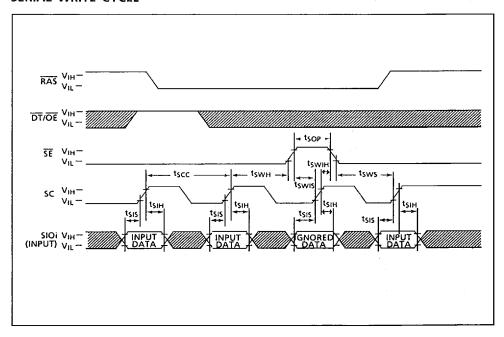

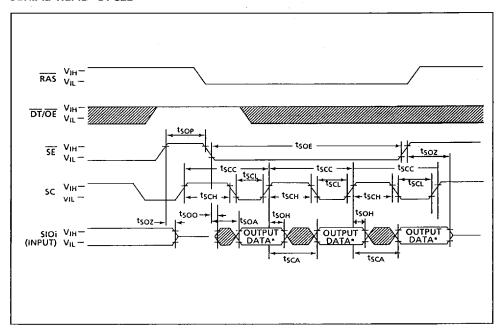

# AC CHARACTERISTICS (CONT.) READ/WRITE, PSEUDO WRITE TRANSFER AND SERIAL READ/WRITE CYCLE

| Parameter                               |                  | - 80 |      | - 10 |      | - 12 |      |    | Notes |

|-----------------------------------------|------------------|------|------|------|------|------|------|----|-------|

|                                         |                  | Min. | Max. | Min. | Max. | Min. | Мах. |    | Notes |

| Serial Clock Cycle Time                 | tscc             | 30   |      | 35   |      | 40   |      | ns |       |

| SC Precharge Time                       | t <sub>SCL</sub> | 10   |      | 10   |      | 10   |      | ns |       |

| SE to Serial Out Setup Time             | tsoo             | 0    |      | 0    |      | 5    |      | ns |       |

| Serial Out Hold after SC High           | t <sub>sOH</sub> | 0    |      | 0    |      | 5    |      | ns |       |

| Serial Output Access Time from SC       | t <sub>SCA</sub> |      | 25   |      | 30   |      | 35   | ns | 16    |

| Serial Output Access Time from SE       | t <sub>SOA</sub> |      | 20   |      | 25   |      | 30   | ns | 16    |

| Serial Output Disable Time from SE High | t <sub>SOZ</sub> |      | 15   |      | 20   |      | 25   | ns | 13    |

| SC Pulse Width                          | t <sub>SCH</sub> | 10   |      | 15   |      | 15   |      | ns |       |

| SE Pulse Width                          | t <sub>SOE</sub> | 10   |      | 10   |      | 10   |      | ns |       |

| SE Precharge Time                       | t <sub>SOP</sub> | 10   |      | 10   |      | 10   |      | ns |       |

| Transfer Command to RAS Setup Time      | t <sub>DLS</sub> | 0    |      | 0    |      | 0    |      | ns |       |

| Transfer Command to RAS Hold Time       | t <sub>RDH</sub> | 60   |      | 75   |      | 90   |      | ns |       |

| Transfer Command to CAS Hold Time       | t <sub>CDH</sub> | 20   |      | 25   |      | 30   |      | ns |       |

| SC to Transfer Command Lead Time        |                  | 10   |      | 15   |      | 20   |      | ns |       |

| SC Hold Time after DT High              |                  | 10   |      | 10   |      | 10   |      | ns |       |

| Serial Data Input to DT High Delay Time | t <sub>SZS</sub> |      | 0    |      | 0    |      | 0    | ns |       |

| DT Precharge Time                       | t <sub>DTP</sub> | 20   |      | 25   |      | 30   |      | ns |       |

| DT to RAS Precharge Time                | t <sub>TRP</sub> | 65   |      | 75   |      | 85   |      | ns |       |

| Serial Write Enable Setup Time          | t <sub>SWS</sub> | 10   |      | 10   |      | 10   |      | ns |       |

| Serial Write Enable Hold Time           | t <sub>SWH</sub> | 10   |      | 15   |      | 20   |      | ns |       |

| Serial Write Disable Setup Time         |                  | 10   |      | 10   |      | 10   |      | ns |       |

| Serial Write Disable Hold Time          | tswiih           | 10   |      | 15   |      | 20   |      | ns |       |

| SC to RAS Setup Time                    | t <sub>SRS</sub> | 15   |      | 20   |      | 20   |      | ns |       |

# AC CHARACTERISTICS (CONT.) READ/WRITE, PSEUDO WRITE TRANSFER AND SERIAL READ/WRITE CYCLE

|                                                | Sym-             | - 80 |      | - 10 |      | - 12 |      | I I mid | Notes |

|------------------------------------------------|------------------|------|------|------|------|------|------|---------|-------|

| Parameter                                      | bol              | Min. | Max. | Min. | Max. | Min. | Max. | 1 1     | Motes |

| Pseudo Transfer Command (SE) to RAS Setup Time | t <sub>ES</sub>  | 0    |      | 0    |      | 0    | _    | ns      |       |

| Pseudo Transfer Command (SE) to RAS Hold Time  | t <sub>EH</sub>  | 20   |      | 20   |      | 20   |      | ns      |       |

| Serial Data In Setup Time                      | t <sub>SIS</sub> | 0    |      | 0    |      | 0    |      | ns      |       |

| Serial Data In Hold Time                       | t <sub>SIH</sub> | 10   |      | 10   |      | 10   |      | ns      |       |

| SC to DT High Setup Time                       | t <sub>SDS</sub> | 0    |      | 0    |      | 0    |      | ns      |       |

| SC to RAS Precharge Setup Time                 | t <sub>SCR</sub> | 0    |      | 0    |      | 0    |      | ns      |       |

#### Notes:

- 1. An initial pause of 200  $\mu$ s is required after power-up followed by a minimum of any 8 RAS cycles (example: RAS-only Refresh) and SC cycles of greater than 8 cycles before proper device operation is achieved.

- I<sub>CC</sub> current depends on the output loading when the output is enabled. ICC (max) is measured with all output open.

- 3. I<sub>CC</sub> current depends on the number of address transitions with CAS held at the V<sub>IH</sub> level. The spec. I<sub>CC</sub> (max) is measured using a maximum of two transitions per address input for each random access cycle and one address change for each Fast Page mode cycle.

- 4.  $V_{IH}$  (min.) and  $V_{IL}$  (max.) are reference levels for measuring the timing of the input signals. Transition times are measured between  $V_{IH}$  and  $V_{IL}$ .

- 5. If clocks are stopped beyond the maximum refresh period of 4 ms a pause of 200  $\mu$ s followed by a minimum of any 8 RAS cycles (example: RAS-only Refresh) is required before proper device operation is achieved.

- 6. The AC measurements assume the transition time ( $t_T$ ) = 5 ns. All AC measurements are made with  $V_{IL}$  (min.) >  $V_{SS}$  and  $V_{IH}$  (max) <  $V_{CC}$  and using a load circuit equivalent of 2 TTL loads with either 50 pF or 100 pF in parallel.

- 7. The spec.  $t_{RCD}$  (max.) is for reference only. The spec  $t_{RCD}$  (min.) =  $t_{RAH}$  (min.) +  $2t_T + t_{ASC}$  (min.)

- Operating within the t<sub>RCD</sub> (max.) limit insures that t<sub>RAC</sub> (max.) can be met. The spec. t<sub>RCD</sub> (max.) is for refrence only. If t<sub>RCD</sub> is greater than the specified t<sub>RCD</sub> (max.) limit, the access time is controlled exclusively by t<sub>CAC</sub>.

- 9. Measured using an equivalent load circuit of 2 TTL loads and 100pF.

- 10. The measurement assumes  $t_{RCD} > t_{RCD}$  (max.).

- 11. Access time is defined by  $t_{CAA}$  rather than  $t_{CAC}$  if  $t_{ASC} < (t_{CAA}$  (max.)  $t_{CAC}$  (max.)  $t_{\overline{1}}$ ).

## TIMING CHART

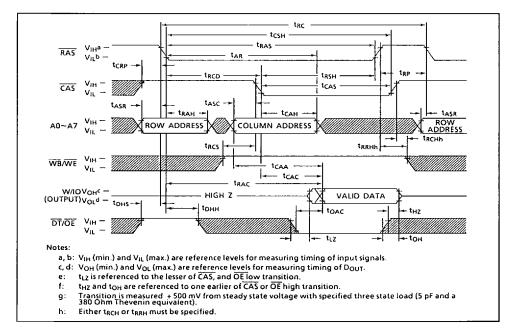

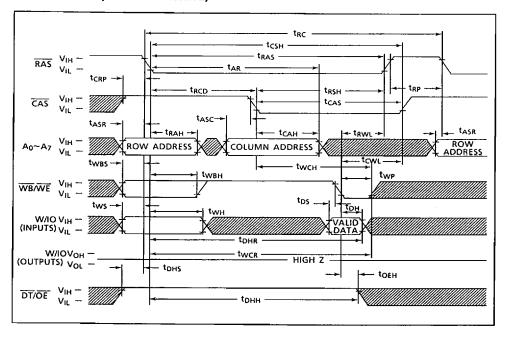

### **READ CYCLE**

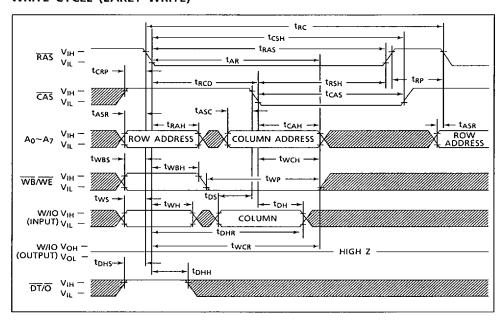

## WRITE CYCLE (EARLY WRITE)

## WRITE CYCLE (DELAYED WRITE)

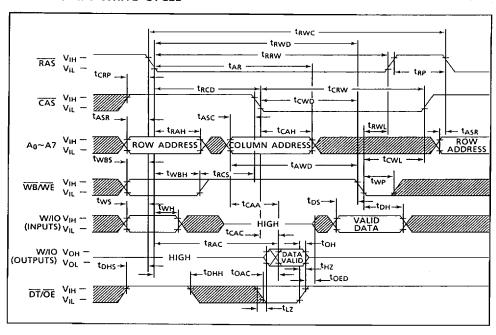

#### **READ-MODIFY-WRITE CYCLE**

11

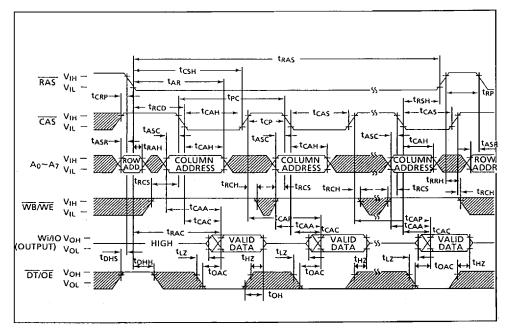

### WAVEFORMS OF FAST PAGE READ CYCLE

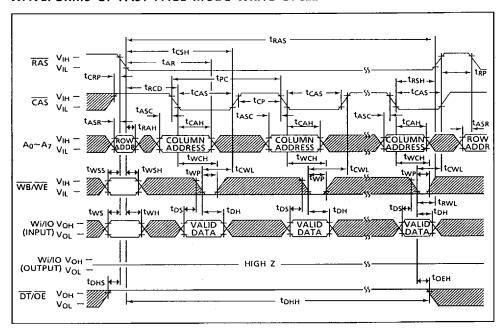

#### WAVEFORMS OF FAST PAGE MODE WRITE CYCLE

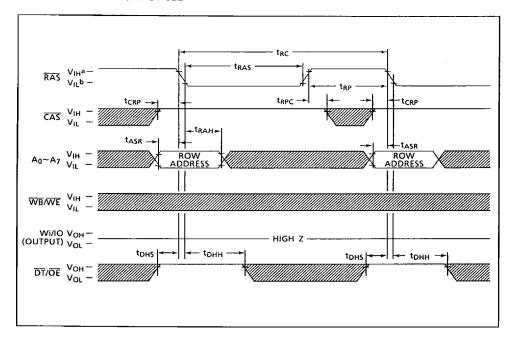

## **RAS-ONLY REFRESH CYCLE**

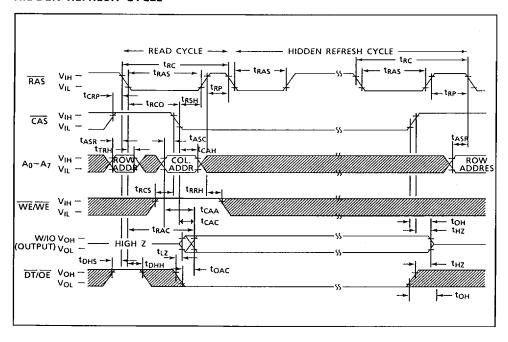

#### HIDDEN REFRESH CYCLE

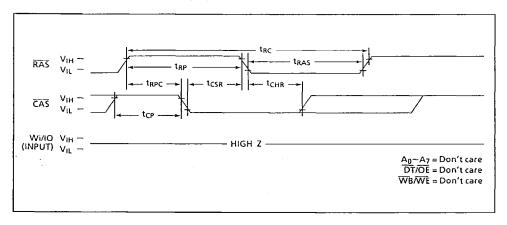

## CAS BEFORE RAS REFRESH CYCLE

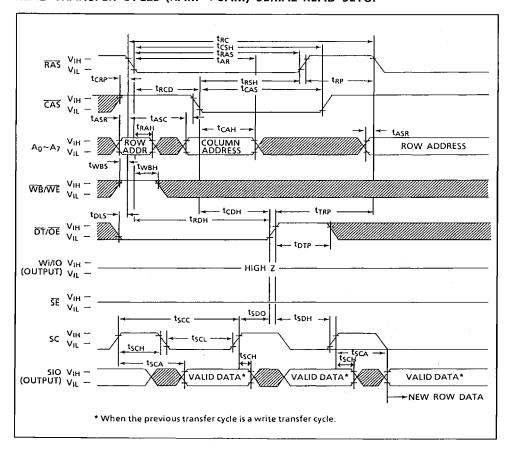

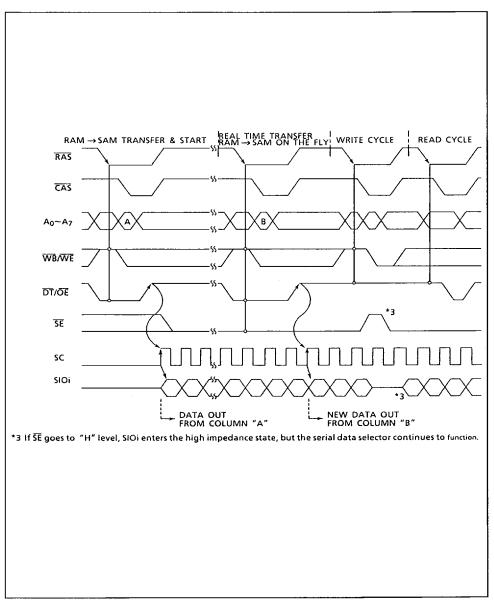

## READ TRANSFER CYCLE (RAM → SAM) SERIAL READ SETUP\*

## READ TRANSFER CYCLE (RAM → SAM)

$\Pi$

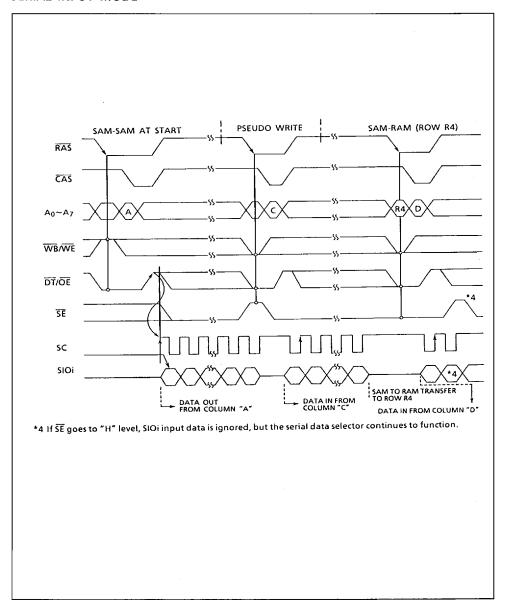

## WRITE TRANSFER CYCLE (SAM → RAM)

## PSEUDO WRITE TRANSFER CYCLE SERIAL WRITE SETUP

## ■ MSM51C262 ■ —

## SERIAL WRITE CYCLE

## SERIAL READ CYCLE

## **BIT MASKED WRITE**

## SERIAL OUTPUT MODE

## SERIAL INPUT MODE

## **FUNCTIONAL DESCRIPTION**

#### **RAM Operation**

The MSM51C262 is a CMOS dynamic memory with 2 ports. One port, the RAM port, operates in the same way as the 64K  $\times$  4 DRAM. The other port, the serial access port (SAM), allows data to be either read from or written to the memory at very high data rates.

The MSM51C262 reads and writes data via the RAM port by multiplexing a 16-bit address into an 8-bit row and an 8-bit column address. The row address strobe (RAS) latches the row address on the chip. The column address, however, flows through the internal column address buffer and is latched by the column address strobe (CAS) signal. Because column access time becomes primarily dependent upon a valid column address rather than the falling edge of CAS, signal timing restrictions on CAS can be greatly loosened with no effect on access time.

### **Memory Cycle**

A memory cycle is initiated by the falling edge of  $\overline{RAS}$ . A memory cycle cannot be ended or cancelled prior to fulfilling the  $t_{RAS}$  (min.) timing specification once it starts. This precaution is necessary for proper device operation and integrity. A new memory cycle cannot be started until the minimum precharge time  $t_{RP}/t_{CP}$  is satisfied.

## Read Cycle

A read cycle is a memory cycle in which data is retrieved from the memory array and presented on the Wi/IOi pins. Read cycles can take the form of single operations to a specific row and column address or page mode accesses to any of 256 column addresses within a single row.

#### Write Cycle

A write cycle is a memory cycle in which data supplied externally to Wi/IOi is written into the location in memory specified by the address. Using the masked write function, any combination of Wi/IOi lines can be written and the remainder ignored. Write cycles can take the form of single operations to a specific row and column address or page mode accesses to any of 256 column addresses within a single row.

## Refresh Cycle

To retain the data in a MSM51C262 DRAM, a refresh operation activating each of the 256 row addresses must be performed at least once every 4 ms. Any operation such as read, write, RMW, RAS-only cycle, CAS before RAS refresh cycle, or transfer cycle refreshes the addressed row.

## **Fast Page Mode Operation**

Fast Page Mode permits an 256 columns of 4 bits within a selected row of the MSM51C262 to be randomly accessed at a high data rate. After a normal cycle initiation, maintaining RAS low while performing successive  $\overline{\text{CAS}}$  cycles retains the row address internally and eliminates the need to resupply it. The column buffer acts as a transparent latch data while  $\overline{\text{CAS}}$  is high and, when  $\overline{\text{CAS}}$  goes low, holds the addresses applied. Because of the transparent latches, the column address flows through and the read access begins upon stable addresses rather than the falling  $\overline{\text{CAS}}$  edge. This eliminates  $t_{\text{ASC}}$  and  $t_{\text{T}}$  from the critical timing path and helps to speed up access while making operation simpler.

During a Fast Page Mode operation, read, write, read-modify-write, or read write-read cycles are possible to random addresses within a selected row. Multiple operations to the same address are permitted as well as more than 256 accesses to any combination of addresses within the selected row. The only limiting factor to the number of such Page Mode accesses is refresh timing. Following the entry cycle into Page Mode, access time is  $t_{CAA}$  or  $t_{CAP}$ -dependent. If the column address is valid before or coincident with the rising edge of  $\overline{CAS}$ ,  $t_{CAP}$  is the access controlling parameter. If the column address is valid after the rising edge of  $\overline{CAS}$ , access time is determined by  $t_{CAA}$ . In both cases, the falling edge of  $\overline{CAS}$  latches the address and enables the output buffers.

With Fast Page Mode, very high sustained data rates can be achieved. The following equation can be used to calculate the data rate possible:

Data Rate =

$$\frac{256}{t_{RC} + 255t_{PC}}$$

#### MODE SELECTION

|                                     |                           | ,,                                   |           | trol Sig  | A <sub>0</sub> ~A <sub>7</sub> |                         |             |             |  |

|-------------------------------------|---------------------------|--------------------------------------|-----------|-----------|--------------------------------|-------------------------|-------------|-------------|--|

| RAM Operation to be<br>Performed    | SAM Mode to be<br>Entered | (Sampled at the falling edge of RAS) |           |           |                                |                         | Sample Time |             |  |

|                                     |                           | CAS                                  | DT/<br>OE | WB/<br>WE | SE                             | W/<br>IO <sub>0~3</sub> | RAS         | CAS         |  |

| Read                                | Mode not affected         |                                      |           | х         | х                              | x .                     | Row         | Column Add. |  |

| Write                               | Mode not affected         |                                      | н         | н         | х                              | х                       | Row         | Column Add. |  |

| Bit Masked Write                    | Mode not affected         |                                      |           | L         | ×                              | н*                      | Row         | Column Add. |  |

|                                     | Mode not affected         |                                      |           | Ĺ         | ×                              | L*                      | Row         | Column Add. |  |

| RAM → SAM Transfer                  | Output Mode               |                                      |           | Н         | х                              | х                       | Row         | SAM Start** |  |

| SAM → RAM Transfer                  | Input Mode                | 1                                    | L         | L         | L                              | х                       | Row         | SAM Start** |  |

| Pseudo Transfer                     | Input Mode                | 1                                    |           | L         | н                              | x                       | Х           | SAM Start** |  |

| CAS-before-RAS or<br>Hidden Refresh | Mode not affected         | L                                    | ×         | ×         | ×                              | х                       | Х           | Х           |  |

#### X = Don't care

- \* The state of the W/IO lines is sampled at the falling edge of RAS to set the Write Bit Mask Register. If W/IO is high at the falling edge of RAS, no masking action is taken and the corresponding data bit is subject to change by a write operation. If W/IO is low at the falling edge of RAS, the corresponding bit is masked and is not altered by a write operation.

- \*\* The 8 address signals, A<sub>0</sub> to A<sub>7</sub>, are used to select the RAM row address that is affected by a transfer to or from the SAM, and the starting address for a SAM read or write operation. The falling edge of RAS strobes the row address, and the falling edge of CAS strobes the SAM starting address.

## **COMBINED RAM-SAM OPERATION**

#### Transfer

The transfer operation of the MSM51C262 allows a row (256 bits) of data to be transferred between RAM and SAM in either direction. The signals and states that control the transfer operation are specified in the Mode Selection Table.

To start a serial write operation, it is necessary to cause the SIO<sub>0</sub> to SIO<sub>3</sub> pins of the SAM, port to be in a high-Z state. The pseudo write transfer cycle accomplishes this and must be performed any time the SAM mode is to be changed from read to write. No data transfer takes place, but addresses are set up as in any other transfer cycle. A read transfer cycle (RAM to SAM) changes the mode from write to read.

#### SAM OPERATION

SAM is organized as 256 words × 4 bits per word. SAM can be loaded from two sources: RAM and the external serial I/O lines, SIOi. SAM has two operational modes, read and write (viewed externally). Mode changes are described in the previous section.

When SAM is in read mode, data is first transferred from RAM to SAM and then can be accessed serially via the SIOi lines, beginning with any SAM address. The progression of data output is from lower to higher numbered bits and addresses are module 256.

When SAM is in write mode, data is captured in SAM by using the SIOi lines, and can be written into a selected row in the RAM by a write transfer operation.

#### Read/Write

The SC pin is used as a shift clock for the SAM port. Serial access is triggered by the rising edge of SC. When SAM is in write mode, the rising edge of SC causes data to be strobed into the selected SAM cell. In the read cycle, output data becomes valid after t<sub>SCA</sub> from the rising edge of SC and remains valid until the next cycle. The SAM address is automatically incremented by SC.

The  $\overline{SE}$  pin is used as an output/input enable pin for the SAM. It does not, however, gate the SC signal, and the SAM address counter for read or write operations continues to increment regardless of the state of  $\overline{SE}$ .

$\Pi$

#### Real-time Read Transfer

The MSM51C262 offers real-time read transfer between RAM and SAM. By using this feature, a continuous data stream can be generated even if the row address must be changed. No loss of timing is caused by this transfer. The data transfer from the RAM to SAM is triggered by the rising edge of DT/OE after the RAS/CAS cycle sets up the data to be transferred and the start address. New row data is available for SAM output after DT/OE returns to a high state in compliance with specification parameters t<sub>SDD</sub> and t<sub>SDH</sub>. SC should be applied continuously and DT/OE timed from SC to achieve non-stop transfer.

### Write Transfer

After SAM is placed in write mode and the required data is captured via SIOi, the write transfer operation causes the SAM content to be written into the selected RAM row. After the write transfer cycle is completed, more data can be written to SAM via SIOi.

#### Power On

After application of the  $V_{CC}$  supply, an initial pause of 200  $\mu$ s is required followed by a minimum of 8 initialization RAS cycles (any combination of cycles containing a RAS clock) and minimum of 8 initialization SC cycles. 8 initialization cycles are required after extended periods of bias without clocks. An extended period of time without clocks is defined as one that exceeds the specified refresh interval. During Power On, the  $V_{CC}$  current requirement of the MSM51C262 depends on the input levels of RAS and CAS. If RAS is Low during Power On, the device goes into an active cycle, and  $I_{CC}$  exhibits current transients. It is recommended that RAS and CAS track with  $V_{CC}$  or be held at a valid  $V_{IH}$  during Power On to avoid current surges.

SIOi after application of the power supply is initialized in the input mode, but this state can not be guaranteed because of the control signal level during power On. Therefore, after  $V_{CC}$  reaches the specified voltage with power On, we recommend to be initialized after carrying out 8 initialization cycles after 200  $\mu$ s.